## 低電壓反相器爲基礎的電壓控制振盪器之特性

#### 沈鼎嵐

輔仁大學電機工程學系

#### 摘 要

本文描述在低電壓環型振盪器中的各種反相放大器對於控制電壓的特性。將 PMOS 的基體端列入考慮,共有六種型式的架構在電源電壓為 0.5 伏特的情況下 觀察其轉移曲線。針對這六種型式放大器所組成的三級環型振盪器使用 CMOS 0.18μm 製程技術模擬其控制電壓對振盪頻率在頻率效能的特性。

**關鍵字:**反相放大器,環型振盪器,基體端。

# Characteristics of Low-voltage Inverter-Based VCOs

## Ding-Lan Shen

Departement of Electrical Engineering Fu Jen Catholic University, New Taipei City, Taiwan

#### Abstract

This paper characterizes the inverted amplifiers which are the definite components of low-voltage ring oscillators with various control voltages. Considering the body terminal of a PMOS transistor, six-type of topologies are observed with their transfer curves at the supply voltage of 0.5V. The frequency performances of 3-stage ring oscillators composed of these six-type amplifiers are simulated in terms of controlled voltage versus oscillating frequency at CMOS 0.18µm technology.

Keywords: inverted amplifier, ring oscillator, body terminal.

E-mail address: dlshen@ee.fju.edu.tw

## 1. Introduction

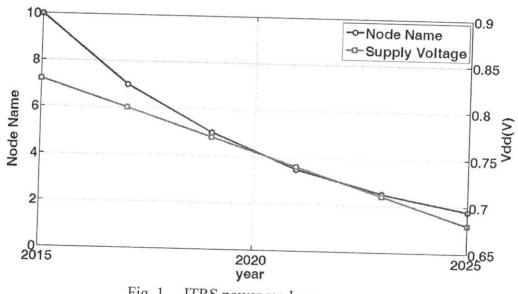

The massive progress of CMOS integrated circuit technology scales not only the feature size but also the supply voltage. With the prediction of International Technology Roadmap for Semiconductors (ITRS) in Fig. 1 [1], the supply voltage will descend toward 0.68V in the year 2025. Nevertheless, due to the performance considerations of digital circuits, the native threshold voltages of transistors are not shrunk accordingly. In such low supply voltage, the inverter based ring oscillators are the conceivable survivors to design the ring voltage-controlled oscillators (VCO) of the phase-locked loop (PLL)[2][3][4]. Because the threshold voltage is near the supply voltage, the body terminal of PMOS is commonly utilized to provide the additional input without scarifying the voltage headroom in ordinary p-well CMOS process [5], [6]. Since the additional freedom of input terminal, there are six major types of inverted amplifiers can be selected to realize the voltage-controlled ring oscillators. This paper analysis the characteristics of these voltage-controlled inverted amplifiers in transfer curves and their tuning range in VCO via simulation.

Fig. 1. ITRS power roadmap.

## 2. Characteristics Description

### 2.1. Conventional Approach

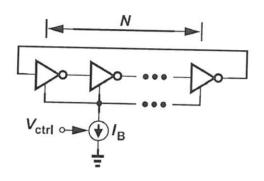

The conventional ring VCOs cascade N-odd stage inverters and control the oscillation frequency through bias current  $(I_B)$  as shown in Fig. 2. The oscillation frequency  $(f_0)$  is given by

$$f_0 = \frac{I_B}{2NV_0C_p},\tag{1}$$

where N is the stage number,  $V_0$  is the amplitude and  $C_p$  is the parasitic capacitance between PMOS and NMOS [7]. The  $I_B$  is determined with the control voltage ( $V_{ctrl}$ ). Nevertheless, the stacked circuits above  $I_B$  limit the conventional development under low supply voltage environment.

Fig. 2. The conventional approach of a ring-oscillator.

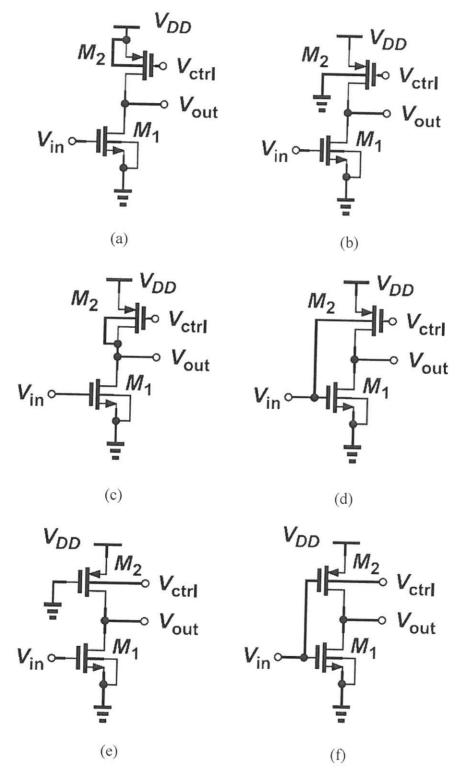

#### 2.2. Body Controlled Inverters

Considering the body effect of a PMOS, the threshold voltage  $(V_{THP})$  is expressed as [8]

$$|V_{THP}| = |V_{THP0}| + \gamma \left( \sqrt{|2\phi_F| + V_{BS}} - \sqrt{|2\phi_F|} \right),$$

(2)

Where  $V_{THP0}$  is the native threshold voltage,  $\phi_F$  is working function, and  $V_{BS}$  is the voltage between body and source. Accordingly, the drain current is altered by gate (G) voltage and body (B) voltage. Since the delay time of a CMOS inverted amplifier is correlated with the drain current, the controlled voltage of the constructed VCO is realized with either gate voltage or body voltage. Base on this principle, six types (type A~F) of the inverted amplifier for a ring-oscillator at low-voltage are depicted in Fig. 3. Type A~D input their controlling voltage,  $V_{ctrl}$ , from the gate of the PMOS. Type A connects the body of the PMOS to the  $V_{DD}$ , type B connects the body of the PMOS to the ground, type C connects the body of the PMOS to the  $V_{out}$ , and Type D connects the body of the PMOS to the  $V_{in}$ . Type E and F input their  $V_{ctrl}$  from the body terminal of the PMOS. Type E connects the gate of the PMOS to the  $V_{in}$ . To characterize the low-voltage properties of these amplifiers, the CMOS 0.18 $\mu$ m technology is applied in the design with a 0.5V

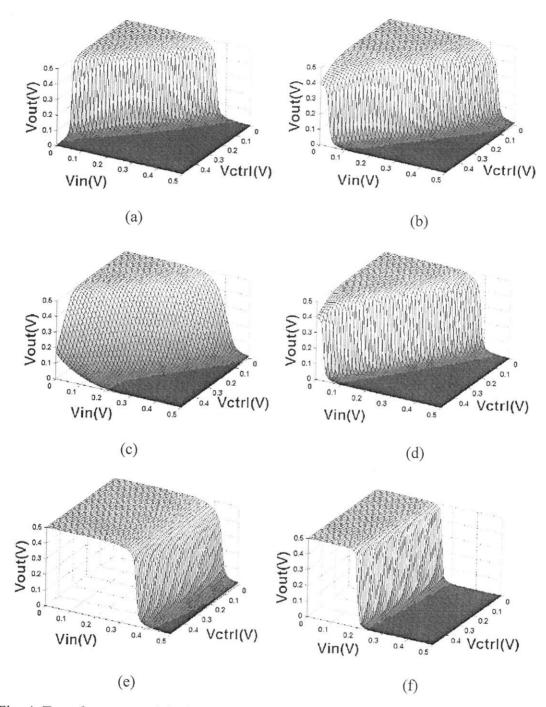

supply voltage. Because all amplifiers except type F are ratio dependent, the W/L of PMOS and NMOS are designed with  $1\mu m/0.72\mu m$  and  $2\mu m/0.18\mu m$  for these six amplifiers. Their corresponding transfer curves with different  $V_{ctrl}$  in the dc analysis are shown in Fig. 4.

Fig. 3. Inverted amplifiers with considering the body terminals. (a) type A, (b) type B, (c) type C, (d) type D, (e) type E, and (f) type F.

Fig. 4. Transfer curves of the inverted amplifier with various control voltage. (a) type A, (b) type B, (c) type C, (d) type D, (e) type E, and (f) type F.

The threshold is correlated with the drain current and is altered with the source to body voltage in the PMOS. The switching threshold of an inverted amplifier depends on the ratio of the drain currents between PMOS and NMOS. This drain current of a MOS transistor is dominated with the gate to source voltage. Therefore, switching threshold of these inverted amplifiers with controlled voltage at the gate of the PMOS (type A~D) is more sensitive than those with controlled voltage at the body of the

Fig. 5. 3-stage voltage controlled ring oscillator.

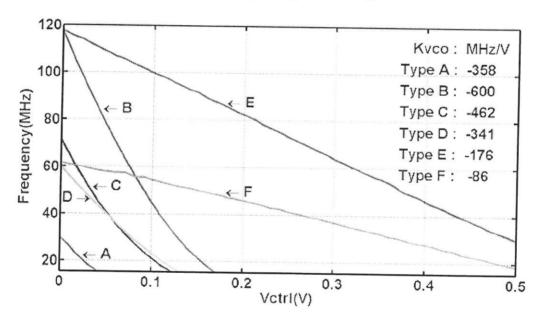

It should be noted that although the inverted amplifiers (type A~D) with higher  $V_{ctrl}$  are still with the functionality of inverting characteristic in the dc analysis, the small  $|V_{GS}|$  causes the PMOS transistor almost off. Consequently, the weak current cannot perform fast switching due to the parasitic capacitances. When connecting three stages of the six-type inverted amplifiers as a voltage controlled ring oscillator as shown in Fig. 5, the simulated  $V_{ctrl}$  versus frequency is depicted in Fig. 6.

Fig. 6. Controlling voltage versus oscillation frequency of 6-type ring-oscillators.

Because the body of the PMOS in type A inverted amplifier is tied to  $V_{DD}$ , the magnitude of its threshold voltage is as the ordinary PMOS device. Therefore, when the  $V_{ctrl}$  exceeds 0.04V, the PMOS enters the subthreshold region and the oscillation frequency is drop to an ultra-low value as shown in Fig. 6. The body of the PMOS in type B is connected to ground. This approach minimizes the magnitude of the threshold voltage of the PMOS and gets a wider tuning range than type A. Nevertheless, the oscillation frequency still drops when  $V_{ctrl}$  is higher than 0.18V. Type

C and D amplifiers tie their body of the PMOS to the  $V_{out}$  and  $V_{in}$ , respectively. Accordingly, the magnitudes of their threshold voltage are between type A and B amplifiers. Their characteristics are similar in tuning range and their duration of the oscillation frequencies are between type A and B amplifiers. Type E and F amplifiers input their  $V_{ctrl}$  through their bodies. Because the body-driven circuits only affect the threshold voltage, their drain current does not strongly correlated with the  $V_{ctrl}$ . Their shape of transfer curves are less altered with  $V_{ctrl}$  in Fig. 4(e) and Fig. 4(f). Consequently, their tuning range achieves wide inputs without suffering from overcoming the threshold voltage as shown in Fig. 6. The type E is pseudo-NMOS type amplifier. Its input capacitance is only derived from the NMOS. Therefore, the input capacitance of type E is smaller than type F. Observing from Fig. 6 the magnitude of  $K_{vco}$  of type E is almost twice than type F with the same aspect ratio. Nevertheless, type E dissipates the static power during the NMOS is ON. The power consumption of type E is larger than type F at the same oscillation frequency. The simulation results indicate that the average power dissipation of type E and type F are 588nW and 453nW respectively at the oscillation frequency of 50MHz.

#### 3. Conclusion

In this work, six types of inverted amplifier are characterized with the transfer curves and the  $K_{vco}$ s in oscillation. The simulation results reveals that the transfer curves and  $K_{vco}$ s are varied more severely with controlled voltage at the gate of PMOS while their control ranges are quite limited. The largest  $K_{vco}$  is obtained with the body tied to ground. The transfer curves and the  $K_{vco}$  are altered gently with wide controlled range when the controlled voltages are applied at the bodies of PMOSs. The  $K_{vco}$  is larger with pseudo-NMOS approach while at the cost of higher power dissipation. These characteristics provide a guidance of designing a low-voltage ring oscillator with inverted amplifiers.

#### References

- [1]. (2015) ITRS reports 2013 update, International Technology Roadmap for Semiconductors. [Online]. Available: <a href="http://www.itrs.net/">http://www.itrs.net/</a>

- [2]. S. Min, T. Copani, S. Kiaei, and B. Bakkaloglu, "A 90-nm CMOS 5-GHz Ring-Oscillator PLL With Delay-Discriminator-Based Active Phase-Noise Cancellation," IEEE Journal of Solid-State Circuits, vol. 48, no. 5, pp.1151-1160, May 2013.

- [3]. Y.-L. Lo, W.-B. Yang, T.-S. Chao, and K.-H. Cheng, "Designing an

- ultralow-voltage phase-locked loop using a bulk-driven technique," IEEE Transaction on Circuits and System. II, vol. 56, no. 5, pp. 339-343, May 2009.

- [4]. Z. Cao, Y. Li, and S. Yan, "A 0.4 ps-RMS-Jitter 1-3 GHz Ring-Oscillator PLL Using Phase-Noise Preamplification," IEEE Journal of Solid-State Circuits, vol. 43, no. 9, pp.2079-2089, Sep. 2008.

- [5]. P.-H. Hsieh, J. Maxey, and C.-K. K. Yang, "Minimizing the Supply Sensitivity of a CMOS Ring Oscillator Through Jointly Biasing the Supply and Control Voltages," IEEE Journal of Solid-State Circuits, vol. 44, no. 9, pp.2488-2495, Sep. 2009.

- [6]. X. Yi, C. C. Boon, M. A. Do, K. S. Yeo, , and W. M. Lim, "Design of ring-oscillator-based injection-locked frequency dividers with single phase inputs," IEEE Microwave and Wireless Components Letters, vol. 21, no. 10, pp. 559-561, Oct. 2011.

- [7]. N. Retdian, S. Takagi, and N. Fujii, "Voltage controlled ring oscillator with wide tuning range and fast voltage swing," in Proc. IEEE Asia-Pacific Conference on ASIC, Taipei, Taiwan, Aug. 2002, pp. 201-204.

- [8]. B. Razavi, Design of Analog CMOS Integrated Circuits. McGRAWHILL, 2001.